# Lehrstuhl für Informatik 1 Friedrich-Alexander-Universität Erlangen-Nürnberg

# **MASTER THESIS**

# Isolation of Operating System Components with Intel SGX

Lars Richter

Erlangen, May 30, 2016

Examiner: Prof. Dr. Felix Freiling

Advisor: Dr.-Ing. Tilo Müller

Advisor: Johannes Götzfried, M. Sc.

| Eidesstattliche Erklärung | / Statutory | <b>Declaration</b> |

|---------------------------|-------------|--------------------|

|---------------------------|-------------|--------------------|

Hiermit versichere ich eidesstattlich, dass die vorliegende Arbeit von mir selbständig, ohne Hilfe Dritter und ausschließlich unter Verwendung der angegebenen Quellen angefertigt wurde. Alle Stellen, die wörtlich oder sinngemäß aus den Quellen entnommen sind, habe ich als solche kenntlich gemacht. Die Arbeit wurde bisher in gleicher oder ähnlicher Form keiner anderen Prüfungsbehörde vorgelegt.

I hereby declare formally that I have developed and written the enclosed thesis entirely by myself and have not used sources or means without declaration in the text. Any thoughts or quotations which were inferred from the sources are marked as such. This thesis was not submitted in the same or a substantially similar version to any other authority to achieve an academic grading.

Der Friedrich-Alexander-Universität, vertreten durch den Lehrstuhl für Informatik 1, wird für Zwecke der Forschung und Lehre ein einfaches, kostenloses, zeitlich und örtlich unbeschränktes Nutzungsrecht an den Arbeitsergebnissen der Arbeit einschließlich etwaiger Schutz- und Urheberrechte eingeräumt.

| Erlangen, May 30, 2016 |             |

|------------------------|-------------|

|                        |             |

|                        | Lars Richte |

### Zusammenfassung

Der Schutz eines Computersystems vor bösartigen Programmen und der Abschottung der Programme gegeneinander stellt seit jeher hohe Anforderungen an Entwickler, Softwarearchitekten und Forscher. Viele verschiedene Versuche wurden unternommen, moderne Computersysteme sicher zu gestalten, doch hoch spezialisierte Angriffe durchdringen auch diese Schutzmechanismen. Mit der zunehmenden Verlagerung von Systemen in fremde Rechenzentren gewinnt zusätzlich ein weiterer Angriffsvektor an Bedeutung, denn nur wenige Schutzmechanismen gehen von einem bösartigen Host-Betriebssystem aus.

Intel hat 2013 mit den Software Guard Extensions (Intel SGX) ein Modell vorgestellt, welches die Informationssicherheit in dem Bereich revolutionieren könnte. An statt das Betriebssystem gegen Anwendungen abzusichern, wird nun die Anwendung unter anderem gegen privilegierten Zugriff des Betriebssystems geschützt. Intel SGX erlaubt es einen vertrauenswürdigen Container zu erstellen, welcher weder vom Betriebssystem noch von anderen Applikationen modifiziert und ausgelesen werden kann. Mit der Veröffentlichung der SGX-fähigen Prozessoren im Oktober 2015 und der notwendigen Entwickler-Tools im Januar 2016 ist es möglich erste Anwendungen für SGX zu entwickeln.

Die Forschung um die Intel Software Guard Extensions befindet sich in den Anfängen. Aus diesem Grund ist eine kritische Auseinandersetzung mit dem Design und Implementation von Intel SGX notwendig. In dieser Arbeit wird Intel SGX analysiert, auf die Grenzen hin getestet und auf die Nutzbarkeit geprüft. Erste Anwendungsfälle werden vorgestellt und kritisch bewertet.

Es wird erstmalig der Ansatz vorgestellt Betriebsystemkomponenten des Linux Kernels mit Intel SGX abzusichern. Das System *TresorSGX* wird beschrieben, welches die Funktionalität eines Kernel Modules in ein geschützten SGX Container auslagert und damit dieses Modul gegen unberechtigten Zugriff absichert. TresorSGX bietet in einem Kernel Modul eine Verschlüsselungsmethode für die Linux Crypto API an, welche geschützt in einem SGX Container ausgeführt wird. Mit diesem System ist der Schlüssel des Algorithmus zu keiner Zeit auslesbar. Es ist dadurch resistent gegen *cold-boot* und *DMA* Angriffe.

Die daraus gewonnenen Erkenntnisse über das Auslagern von Kernel Komponenten in SGX Container können als Basis für künftige Forschungsthemen in dem Umfeld dienen.

#### **Abstract**

The defence of a computer system against malicious applications and the isolation of applications against each other has always been a challenge for developers, software architects and researchers. Different attempts were made to design secure systems. However, highly sophisticated attacks manage to overcome those security measurements. With the migration of computer systems into foreign datacenters another attack vector gains influence because only a few safety mechanisms take malicious host operating systems into consideration.

In 2013 Intel proposed the Software Guard Extensions (SGX) as new model to secure applications. Instead of securing the operating system against applications the applications are protected against privileged unauthorised access. Intel SGX provides a secured trustworthy container which cannot be accessed, read or modified by any unauthorised party. With the release of the SGX-capable processors in October 2015 and the required developer tools in January 2016 it is possible to develop first SGX applications.

The research about the Intel Software Guard Extensions is in the very beginning. Therefore, a critical examination of the design and implementation of SGX is required. In this thesis SGX will be analysed, its limits tested and the usability examined. Available use cases for SGX will be presented and critically evaluated.

A new attempt to isolate and secure operating system components of the Linux kernel will be introduced. The system *TresorSGX* which outsources a functionality of a kernel module to a SGX container will be described. TresorSGX provides a cryptographic algorithm for the Linux Crypto API which is executed in a secured container. The cryptographic key material is guarded from unauthorised access of unprivileged and privileged components at any time. This protects the disk-encryption system from *cold-boot* and *DMA* attacks.

The gained insights about the migration of kernel components into SGX containers can serve as foundation for future research in that field.

# **CONTENTS**

| 1. | Intro | ductio   | n                                          | 1  |

|----|-------|----------|--------------------------------------------|----|

|    | 1.1.  | Motiva   | tion                                       | 2  |

|    | 1.2.  | Task .   |                                            | 4  |

|    |       | 1.2.1.   | Analysis of SGX                            | 4  |

|    |       | 1.2.2.   | SGX in Linux Kernel                        | 4  |

|    |       | 1.2.3.   | Tresor with SGX                            | 5  |

|    | 1.3.  | Related  | d Work                                     | 5  |

|    | 1.4.  | Results  | 3                                          | 5  |

|    | 1.5.  | Outline  |                                            | 6  |

|    |       |          |                                            |    |

| 2. |       | kgroun   |                                            | 9  |

|    | 2.1.  | Intel So | GX                                         | 10 |

|    |       | 2.1.1.   | Motivation                                 | 10 |

|    |       | 2.1.2.   | History                                    | 11 |

|    |       | 2.1.3.   | Related Approaches to Trusted Computing    | 12 |

|    |       | 2.1.4.   | SGX Security Characteristics               | 18 |

|    |       | 2.1.5.   | Technology                                 | 19 |

|    |       | 2.1.6.   | SGX SDK                                    | 29 |

|    |       | 2.1.7.   | SGX Availability                           | 34 |

|    |       | 2.1.8.   | Use Cases                                  | 36 |

|    |       | 2.1.9.   | Attacks on Enclaved Systems / Untrusted OS | 39 |

|    |       | 2.1.10.  | Limitations of SGX                         | 40 |

|    |       | 2.1.11.  | Future of SGX                              | 41 |

|    | 2.2.  | OpenSo   | GX                                         | 42 |

|    |       | 2.2.1.   | Motivation                                 | 43 |

|    |       | 2.2.2.   | Architecure                                | 43 |

|    |       | 2.2.3.   | Limitations                                | 45 |

|    | 2.3. | Linux Kernel                         | 45 |

|----|------|--------------------------------------|----|

|    |      | 2.3.1. Architecture                  | 46 |

|    |      | 2.3.2. Interaction with User space   | 47 |

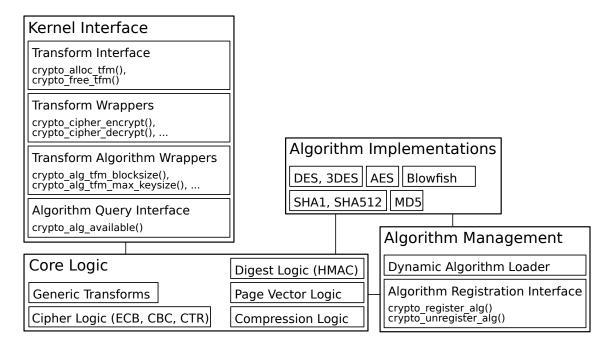

|    |      | 2.3.3. Crypto API                    | 48 |

| 3. | Tres | orSGX                                | 53 |

|    | 3.1. | Motivation                           | 53 |

|    |      | 3.1.1. Original Tresor               | 54 |

|    |      | 3.1.2. Benefits of SGX               | 54 |

|    | 3.2. | Design                               | 55 |

|    |      | 3.2.1. Enclave Management            | 55 |

|    |      | 3.2.2. Communication with Crypto API | 56 |

|    |      | 3.2.3. Enclave Cryptography          | 56 |

|    | 3.3. | Implementation                       | 57 |

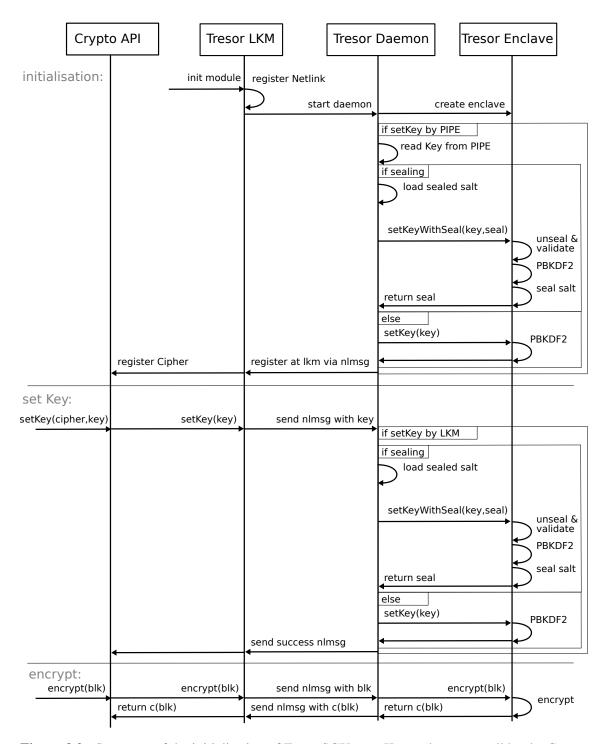

|    |      | 3.3.1. Lifecycle                     | 58 |

|    |      | 3.3.2. Kernel Module                 | 61 |

|    |      | 3.3.3. Daemon                        | 67 |

|    |      | 3.3.4. Enclave                       | 68 |

|    |      | 3.3.5. Usage                         | 70 |

| 4. | Eval | uation                               | 73 |

|    | 4.1. | TresorSGX usage                      | 73 |

|    | 4.2. | Correctness                          |    |

|    | 4.3. | Performance                          | 75 |

|    |      | Security                             | 76 |

| 5. | Con  | clusion and Future Work              | 79 |

| -  |      | SGX Development                      | 79 |

|    |      | SGX Enabled Tresor                   | 80 |

|    |      | Isolation of OS Components with SGX  | 81 |

|    |      | Future Work                          | 81 |

| Δn | pend | lices                                | 83 |

| ~~ | Pont |                                      | 50 |

| A. | Bac  | kground                              | 85 |

|    | ۸ 1  | Intal SCY                            | 25 |

# CONTENTS

| В.  | Evaluation            | 89 |

|-----|-----------------------|----|

|     | B.1. Performance test | 89 |

| Bil | oliography            | 99 |

1

# INTRODUCTION

The protection of a computer system against malicious applications and the isolation of software components has been a difficult task for software developers, software architects and researchers since the beginning. Many attempts were made to secure modern systems but the rising complexity and dependency of big applications allow highly sophisticated attacks to succeed. With the current trend of outsourcing the physical layer or operating system layer of a datacenter to foreign resources another attack vector is rising because most security considerations assume that the physical layer can be trusted.

When discussing security related topics the broad term *security* has to be explained at first. Its meaning depends heavily on the field where it is applied. In general, the security guarantees that an asset is defended against a set of attacks. The asset can be the system itself or information. The attacker is trying to interfere with the security properties of the asset.

The basic security properties of an asset are *Confidentiality*, *Integrity*, *Availability* and *Authenticity*. The confidentiality guarantees that the asset can not be obtained by an unauthorized entity. A standard measure to achieve confidentiality is to encrypt sensitive data. The encryption keys itself become confidential assets too. The second security property is the integrity of data. Data must be complete and not be modified by an unauthorized entity. By using hashing and signature techniques alternations of data can be detected. The availability of an asset guarantees that an user can access the information or the system if he needs to. A classic attack against availability is the denial-of-service attack which

leads to a complete unavailability of the system. By using redundancy and additional security measures the availability can be increased. The authenticity of an asset gains more and more significance. It ensures that the asset can proove its identity and its properties against a challenging user. If an attacker tries to impersonate the asset, the user will detect it. In the world wide web authenticity is guaranteed by using public key cryptography and digital certificates. The user trusts root certificate authorities and therefore trusts entities which proof their identity by signing with issued certificates. These basic security properties are applied to the trusted computing field too.

In 2013 Intel published the Intel Software Guard Extensions (Intel SGX) in a series of papers Hoekstra et al. [20] McKeen et al. [44] Anati et al. [1]. They proposed a new programming model which uses containers, so called *enclaves*, which can only be accessed by the CPU and no other party of the system. Furthermore neither the operating system nor a hypervisor can read the content of the enclave at runtime. In the light of the current movement into the *Cloud* this programming model looks really promising to retain the security, integrity and confidentiality of on-site datacenters.

The Intel Skylake processor, released in October 2015, allows the creation and execution of SGX enclaves via its extended instruction set. Multiple researchers published first ideas and proof of concepts of how applications can benefit from SGX Kim et al. [37]Baumann et al. [3]Ohrimenko et al. [48].

# 1.1. Motivation

The most of the security systems and security analysis assume that the host system can be trusted and that an attacker enters the system from the outside, for example the network or the periphery of the computer. Even if a malicious application is executed at the system, most of the research assume that at least the operating system can be trusted. Because of malware that affects the hypervisor and recurring security vulnerabilities in operating systems it becomes clear that this assumption can not be trusted any longer when our daily live depends on numerous computing systems.

Furthermore mobile devices are available which allow the execution of security critical applications like online banking. These platforms are becoming more and more open that users are able to install custom applications and operating systems, downloaded from the internet. These applications can be malicious to either trick the user to insert confidential information or to exploit other applications on the device.

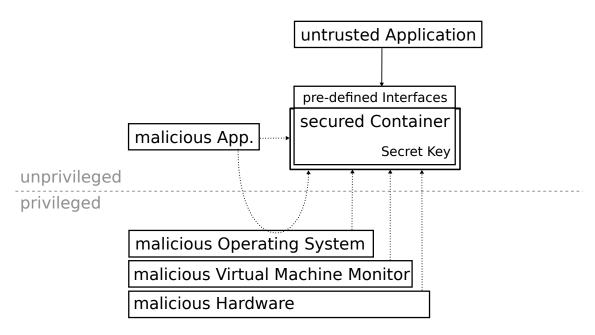

The security model of Intel SGX assumes that only the CPU can be trusted and other applications and the host operating system per se can be malicious as shown in Figure 1.1. Secured containers (trusted enclaves) can be loaded into a protected memory area which can only be accessed by the CPU. No malicious application, operating system or virtual machine monitor can access the information in the secured container. The memory of the container is encrypted in the CPU to defend against observation via the hardware. These

**Figure 1.1.:** The secured container defends against unauthorized access and allows access only over pre-defined interfaces

containers (enclaves) can be attested and remotely verified that they are unmodified. This allows the distribution and execution of trusted enclaves at scale.

The Intel software guard extensions have the potential to overcome known problems and risks regarding critical applications at unknown hosts. Intel itself proposed use cases for the new technology Hoekstra et al. [20]. They developed a software based *one-time* password token generators and secured Enterprise Rights Management Clients. Other researchers developed a model to remote attestate routing controllers of the Tor network to guarantee their integrity. Other use cases and filed patents will be discussed in section 2.1.8.

A custom enclave can only be launched with a special Launch Enclave from Intel. This fact was discovered during the examination of the SGX documentation in late 2015. At that time the only possibility to gain experience with the SGX software model was to use the OpenSGX emulator [15]. Since January 2016, the SGX SDK for Windows was made available to the public, allowing practical research based on real hardware.

The main use case for SGX is to include small functions into the enclave to harden the codebase against different attacks. In this thesis SGX is used to improve the security of the Linux Kernel. With TRESOR Müller et al. [46], Crypto API implementation of AES, it is able to withstand cold boot attacks on memory. This approach will be continued with the Software Guard Extensions. Instead of saving the cryptographic key material in CPU registers, the key will be saved in an enclave. This use case is the basis of a first proof of concept for the usage of Intel SGX in the Linux Kernel.

# 1.2. Task

The task of this thesis is divided into three main parts. In the beginning there has not been an official documentation apart from the SGX white papers and the Instruction Set Reference. During the elaboration of the thesis more and more official documentation were published.

# 1.2.1. Analysis of SGX

The first task was to analyse SGX from the 2013 white papers Hoekstra et al. [20] McKeen et al. [44] Anati et al. [1] and the Instruction Set Reference Intel [25] which was published in October 2015. Assumptions were made and key facts were left out in these documents. Other researchers reviewed these documents and set them in the context with filed patents Costan and Devadas [11]. In January 2016, the Intel SGX SDK was released and with it additional documentation [27] [28]. These documents give proof about the assumptions researchers made about the Intel Launch Enclave.<sup>1</sup>

The details about SGX are well described in these sources. The scope of this thesis is not to describe SGX into detail but to describe how the theory about SGX is applied in reality. The technology behind SGX will be described at a higher level to create understanding of SGX, its mechanics, the tools and the software model.

The use cases for SGX will be discussed based on patents that were filed by corporations. With the help of these patents it is possible to give an overview about the usage of SGX and its possible future field of application. Today it is unknown if an licensing scheme exists. Furthermore requirements for optaining production SGX certificates will be discussed.

#### 1.2.2. SGX in Linux Kernel

In contrast to secure user mode applications against other user mode applications, this approach is using SGX to secure Linux kernel modules. Similar to a microkernel should be the kernel components isolated from each other. The goal is that even with a vulnerability in a kernel module, it is not possible to gain power over other modules by exploiting this vulnerability. With SGX it is possible to build resistant components which can not be exploited by privileged malicious applications.

However, in the official documentation of Intel SGX it is stated that the new instructions can be differentiated in privileged and unprivileged instructions. During the analysis of SGX it became clear that SGX is not built to enter enclaves from kernel mode. Instructions that are used to enter an enclave and execute enclave functions are not available in ring-0 [25]. Therefore SGX is used in a detour to the user space.

$<sup>^1</sup> https://jbeekman.nl/blog/2015/10/intel-has-full-control-over-sgx/\\$

#### 1.2.3. Tresor with SGX

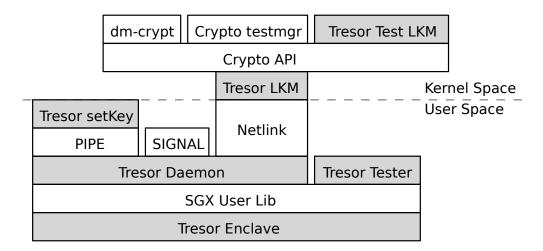

The SGX enabled Tresor extends the Tresor by Müller et al. [46]. It is meant to be a proof of concept of isolation kernel functions. As previously described it was first planned to implement TresorSGX fully in the kernel space. Because of the findings about SGX, a three layered architecture is used to provide kernel module functionality by executing SGX in user mode.

# 1.3. Related Work

Intel SGX is a new technology. The required tools for executing SGX enclaves on hardware are just released in January 2016. Therefore, the published papers which discusses SGX and proposes possible use cases are limited. Papers and patents regarding use cases for enclave systems are discussed in section 2.1.8. A recommended paper which analyses the available Intel SGX documentation and Intel SGX patents is published by Costan and Devadas [11].

# 1.4. Results

This thesis is a first analysis of the possible usage of SGX in kernel space. During this elaboration the available SGX capable hardware and software changed, which resulted in changing requirements too.

**Intel SGX** has been compared to other technologies and its history has been outlined. Furthermore, a hands on experience with the SGX SDK has been described. With the help of examples its functionality and components have been described in detail. Furthermore, the current situation of SGX capable hardware and the limitations of SGX have been highlighted. Based on filed patents different use cases of SGX have been shown and discussed. In addition, a final outlook of the future of Intel SGX has been made build on these patents and the documentation.

**Tresor SGX** The TresorSGX architecture is a proof of concept of isolating kernel modules using Intel SGX enclaves. TresorSGX registers a cipher at the Crypto API to support encryption tools like dm-crypt. The encryption key of the TresorSGX cipher is at no time receivable by any privileged or unprivileged processes. The key is generated using sealing techniques discussed later in this thesis. This makes the cipher sturdy against cold-boot and DMA attacks. Furthermore, it is not possible to recover the key by modifying any component of the untrusted TresorSGX architecture.

The functionality of the original Tresor has been exceeded. The encryption key is not retrievable at any point. However, the additional software layers are causing a limited throughput.

#### 1.5. Outline

**Background** At first the Intel Software Guard Extensions will be discussed in section 2.1. Afterwards a time line of the published SGX hardware, software and documents is presented in section 2.1.2. These SGX components were made available during the elaboration of this thesis. In section 2.1.3 an overview about other approaches on trusted computing, their benefits and disadvantages in comparison with Intel SGX is given. The security benefits of SGX are discussed in the section 2.1.4.

The techniques that are used by the Intel Software Guard extensions are described in section 2.1.5. Also the steps, tools and generated files which are used to create an enclave are discussed in that section. With the knowledge of the characteristics and technology, an overview about the software development kits (SDK) is given in section 2.1.6. The next section 2.1.7 describes the hard- and software requirements for SGX and the current state of SGX availability. The Intel SGX section is finalised with the section 2.1.8 about use cases and published patents regarding SGX and similiar technologies. In section 2.1.11 the possible future usage of SGX is discussed.

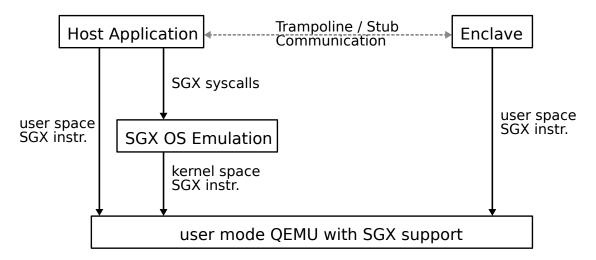

The section OpenSGX 2.2 describes the QEMU based Emulator for SGX like Enclaves. An insight into the architecture, limitations and differences to Intel SGX is given. OpenSGX has been used in the first half of the development phase of the SGX enabled Tresor but has been abandoned with the access to the Intel SGX SDK. However, OpenSGX provides nearly the same programming experience as Intel SGX without the need for SGX capable hardware. Furthermore it is possible to debug the complete emulated system, which allows a deeper understanding of the architecture.

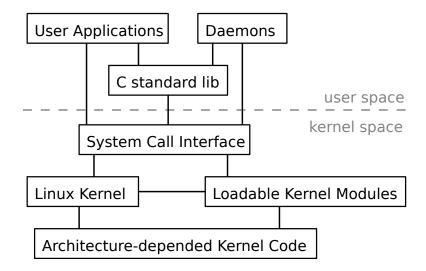

The third part of the background chapter analyses the Linux kernel 2.3. During the analysis phase of Intel SGX different insights how SGX works and how it can be used became apparent. That lead to a higher complexity in the implementation. The differencies of the kernel- and usermode 2.3.1, the interaction and communication between these two modes will be discussed. Also the interfaces and workflow of the Linux Kernel Crypto API 2.3.3 will be analysed.

**Design and Implementation** Based on these findings about Intel SGX, OpenSGX and the Linux Kernel the implementation of the SGX enabled Tresor is described in section 3. After a motivation and short review on the original Tresor the benefits of using the SGX are portrayed in section 3.1.2. The design section 3.2 describes the considerations regarding enclave management, user to kernel communication and cryptography components.

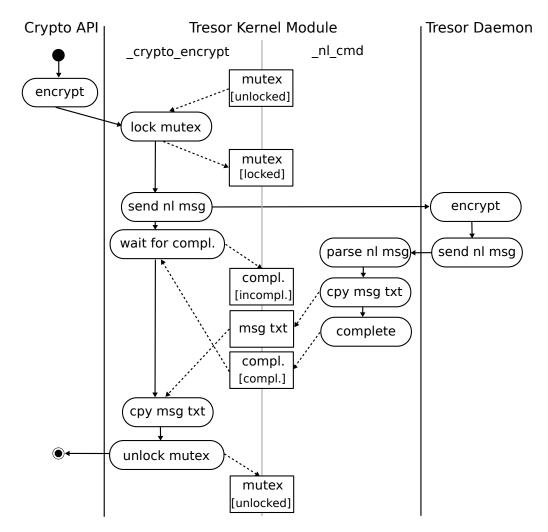

The implementation of TresorSGX is described in section 3.3. After the architectural overview the enclave lifecycle is shown. The different components of the TresorSGX Linux Loadable Kernel Module are explained in 3.3.2. The possibilities to analyse and test the encryption of TresorSGX by using the Linux Crypto API testmanager are described in section 3.3.2 and by using the custom kernel module in section 3.3.2.

The user space component which communicates with the kernel module is the TresorSGX daemon and is discussed in section 3.3.3. The daemon communicates with the enclave which is explained in section 3.3.4. The usage of TresorSGX is explained in section 3.3.5. Information about the mandatory components of TresorSGX and about the setup of an encrypted partition are given there.

**Evaluation** The chapter 4 analyses how the initial motivation and expectations for the SGX enabled Tresor implementation matches the results. At first the usability of TresorSGX is analysed in section 4.1. This is followed by section 4.2 which discusses the correctness of the encryption and compatibility with other cryptography ciphers. In section 4.3 the performance of TresorSGX iscompared to plain usage and the standard aes encryption. The chapter ends with section 4.4 about the security properties of TresorSGX.

**Conclusion and Future Work** The limitations of the Software Guard Extensions are discussed in section 5.1. The observed limitations and acknowledgement during the design and implementation of TresorSGX are discussed in section 5.2. The findings about the usage of SGX to isolate OS components are finalised in section 5.3. An outlook to future work is given in section 5.4.

2

# **BACKGROUND**

The Intel SGX capable Hardware and the Intel SGX SDK were made available just recently. A top down approach is used to describe Intel SGX in the following. This way a comprehension of the development model is created without the need to read through the complete Intel SGX Instruction Set Reference manual [25]. For deeper understanding of the mechanics important references will be given at any point. Also the paper by Costan and Devadas [11] is recommended for a more detailed description of the Intel Software Guard Extensions.

Because of the missing hard- and software (described in detail in section 2.1.7) during the first part of the research, the emulator OpenSGX was used and will be discussed in section 2.2. However, OpenSGX is only able to emulate user space applications, therefore only the user space part of TresorSGX can be executed in OpenSGX.

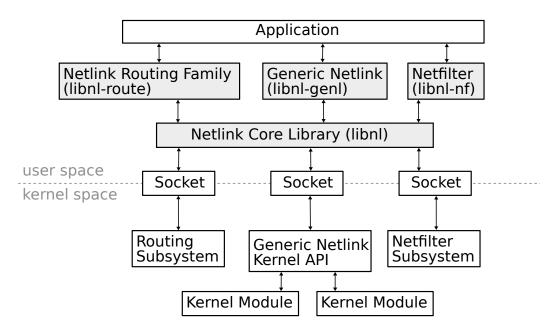

As previously outlined some aspects of the Linux kernel are also described in section 2.3. This section will help to gain some insight into Linux kernel development and the Linux kernel Crypto API. The possibilities of user to kernel space communication are also discussed and lead to the implementation of the Netlink interface.

# 2.1. Intel SGX

The Intel Software Guard Extensions is a technology which provides high level protection of data and was first published in 2013 as Innovative Instructions and Software Model for Isolated Execution [44], Using Innovative Instructions to Create Trustworthy Software Solutions [20] and Innovative Technology for CPU Based Attestation and Sealing [1].

With Intel SGX it is possible to create containers in protected memory as shown in Figure 1.1. This container is called an *enclave*. It is not possible to read or write in that protected memory from the outside of the enclave. The enclave provides integrity and availability of its data even if it is executed on a malicious host. The code of an enclave can be executed by special instructions which are available on Intel's newest generation of Skylake CPU's that were released in September 2015. The first batch of Skylake CPUs was not able to execute SGX. Only post-conversion CPUs that were made available on October 26, 2015 support SGX [29]. The special instructions are described in section 2.1.5.

In the following sections the motivation and other approaches which were created to secure the execution and the data of an application are discussed. Furthermore, the technology, architecture and software which is used by Intel SGX, is described. To put the theoretical background in relation with the reality, SGX is analysed regarding its usage. Based on filed patents and available research papers the future usage of SGX is estimated in section 2.1.8.

#### 2.1.1. Motivation

The higher goal of the Intel Software Guard Extensions is to improve the overall information security on a computing device. This is achieved by securing and schielding the application and its memory against unauthorised access or by guaranteeing the authenticity and integrity of an enclave. The Software Guard Extensions help securing sensitive user passwords, confidential enterprise data and protecting intellectual property. Special use cases and an overview about the future use of Intel SGX based on filed patents can be found in section 2.1.8.

Furthermore, it is possible to use SGX in the cloud computing environment. Users must trust an unknown entity with their data and their applications. The user has no information how the platform provider handels the data, if the platform is secured against any insider or ousider attack or if the platform provider itself has an interest in optaining or modfying the users data.

The strategy is to distribute encrypted containers, which contain both the application and the data, to cloud computing vendors. The container is especially encrypted for that single server CPU in the foreign datacenter. A provisioning enclave can decrypt the data and initialise the enclave. Only the CPU is able to execute the enclave application and to decrypt its memory.

During the loading of an enclave its content is hashed by the CPU. This measurement hash can be used for remote-attestation (which is described in section2.1.5) against a challenger. Remote attestation can be used to verify the other communication party if it is the unmodified application one expect and if it is running in a SGX environment.

# 2.1.2. History

The Intel Software Guard Extensions published their whitepapers during the *The Second Workshop on Hardware and Architectural Support for Security and Privacy*<sup>1</sup> (HASP 2013) in Tel-Aviv in June 2013. The HASP is intented to be a workshop for security research on application level, hardware and architecture aspects in the era of cloud computing.

They at first presented their paper *Innovative Instructions and Software Model for Isolated Execution* [44]<sup>2</sup>. Followed by the paper *Innovative Technology for CPU Based Attestation and Sealing* [1]<sup>3</sup>. Based on this foundation the paper *Using Innovative Instructions to Create Trustworthy Software Solutions* [20]<sup>4</sup> was published.

In September 2013 Intel published the first part of an explainatory series *SGX for Dum-mies*<sup>5</sup> describing eight SGX Design Objectives which will be discussed in section 2.1.4. Part two and three were released in the beginning of the year 2014.

In 2014 Baumann et al. [3] proposed *Haven* which allows the shielded execution of legacy applications on commodity operating systems and hardware. Haven describes a first use-case by Microsoft for the usage of SGX. Another secured architecture proposal was published by Li et al. [39] called *MiniBox*. Google is using MiniBox cross-platform concept for a Platform-as-a-Service cloud computing scenario.

The Intel Software Guard Extensions Programming Reference [25] was published in October 2014. Based on the description of the new instructions and memory operations it was possible to get a deeper understanding of SGX and how Intel wants to achieve their security goals.

In May 2015 Intel informed that SGX protects against memory attacks but not against sidechannels<sup>6</sup>. They are referencing a paper by Xu et al. [63] which allows the extraction of documents and images over controlled-channel attacks. Although the data itself and the memory is not accessable, these sidechannels allow a data reconstruction by observing access and timing patterns. The host application which uses the trusted enclave functions and the internal enclave functions must be hardened against these scenarios.

<sup>&</sup>lt;sup>1</sup>https://sites.google.com/site/haspworkshop2013/

<sup>&</sup>lt;sup>2</sup>Presentation: https://docs.google.com/file/d/0B\_wHUJwViKDaRm00QlVITkYxckE/edit?usp=sharing

<sup>&</sup>lt;sup>3</sup>Presentation: https://docs.google.com/file/d/0B wHUJwViKDaaUhEUjVDcVBYUlk/edit?usp=sharing

<sup>&</sup>lt;sup>4</sup>Presentation: https://docs.google.com/file/d/0B wHUJwViKDaMm9PU3hOTUhLbHM/edit?usp=sharing

<sup>&</sup>lt;sup>5</sup>https://software.intel.com/en-us/blogs/2013/09/26/protecting-application-secrets-with-intel-sgx

<sup>&</sup>lt;sup>6</sup>https://software.intel.com/en-us/blogs/2015/05/19/look-both-ways-and-watch-out-for-side-channels

At the ISCA 2015 Intel presented a set of tutorial slides [26]<sup>7</sup> giving an in-depth architecture, SGX key hierarchy, attestation and provisioning description. They also demonstrated a side channel evaluation tool and gave an overview about the Linux SGX SDK.

The SGX capable CPU generation *Skylake* was released in August 2015<sup>8</sup>. However, SGX was not available at the first batch of Skylake CPU's. This information was published in a product change notification [29] on October 1st 2016, two month after the initial release. The customer should expect *post-conversion* material between October 26th and November 30th. The SGX capable CPU's do not differentiate from the non-capable CPU's. SGX can only be tested during runtime. However, testing SGX during runtime was not possible in 2015 because no SGX BIOS update was available for the desktop mainboards.

In October 2015 a researcher discovered that the *Launch enclave* is a mandatory component in the SGX lifecycle<sup>9</sup>. Only an Intel signed enclave can be startet without a Launch-Key / EINITTOKEN. Without this enclave no custom enclave can be initialised. That *feature* was not highlighted by Intel in the documentation and never mentioned in the SGX whitepapers. However, it is described in the issued patents by Intel. The Launch enclave guarantees that the enclave author is in a business relationship with Intel.

The Windows SGX SDK<sup>10</sup> containing Kernel Drivers, SGX Services and Architectural Enclaves, was published in January 2016. With the help of these tools it is possible to create and launch enclaves on supported machines.

The available SDK's permit an enclave creator to deploy debugging enclaves. For production licences a developer must undergo an evaluation process by Intel described in an article from February 2016<sup>11</sup>. To be granted a production license the developed application must follow defined coding practices. Found vulnerabilities must be fixed in a certain period of time. Additionally, the developers must demonstrate the ability to save the enclave signing key securely following industry best practices. These requirements will be discussed in section 2.1.7.

# 2.1.3. Related Approaches to Trusted Computing

Trusted Computing is a initiative by the Trusted Computing Group (TCG)<sup>12</sup> to enhance PC security. The TCG is a not-for-profit organisation which initially was a consortium of AMD, HP, IBM, Intel and Microsoft. Its goal is to define global industry specifications and standards which increase the security of devices.

Trusted Computing guarantees that the system behaves in predefined deterministic ways. This behavior is enforced by hardware and software. Furthermore, Trusted Computing

<sup>&</sup>lt;sup>7</sup>https://software.intel.com/sites/default/files/332680-001.pdf

<sup>8</sup>https://newsroom.intel.com/chip-shots/chip-shot-intel-unleashes-next-gen-enthusiast-desktop-pc-platform-at-gamescom/

<sup>9</sup>https://jbeekman.nl/blog/2015/10/intel-has-full-control-over-sgx/

<sup>&</sup>lt;sup>10</sup>https://software.intel.com/en-us/sgx-sdk

<sup>&</sup>lt;sup>11</sup>https://software.intel.com/en-us/articles/intel-sgx-product-licensing

<sup>&</sup>lt;sup>12</sup>https://www.trustedcomputinggroup.org/

protects critical data and defends against attacks on the system. It makes secure authentication possible and protects the cryptographic key material and certificates. Also it allows the attestation of the device itself and guarantees its identity. This allows to protect the user against some security risks, but it also hands over control to a third party.

The Electronic Frontier Foundation warns about the possible abuse of the features that come along with Trusted Computing Systems [53]. They state that Trusted Computing not only can be used to defend against malicious applications but it can also be used to defend against the system owner and can enforce policies against its will. A few examples for the negative use of Trusted Computing are application lock-in, forced upgrade, -downgrade and the forced installation of application specific spyware.

In the following some Trusted Computing approaches and individual objectives by different vendors will be discussed. This section provides background information about the past of Trusted Computing and why SGX has been developed the way it is. A complete breakdown of the different systems and a in-depth analysis can be found in [11] and will be referenced.

#### **Trusted Platform Module**

The goal of the Trusted Computing Group was to develop a specification for a standardised module which enables trusted computing features. As a result the specification *ISO/IEC 11889* was created.

Since then the TCG published updates to the original TPM specification. October 2014 the latest TPM release 2.0 was published.

The Trusted Platform Module must be able to perform asymmetric key generation, asymetric encryption / decryption, hashing and random number generation. Furthermore, it must be able to perform three different tasks [60].

- **Remote Attestation** allows to create a hash which depends on the hard- and software configuration of the system. This hash stands as a state of the system and verifies against a third party that the state has not changed.

- **Binding** allows the encryption of data with the public key of the TPM. The data can only be decrypted by using the secret key inside the TPM. Therefore, the data is bound to the TPM. A practical use case for binding is the provisioning of certificates and encryption keys.

- **Sealing** allows to use binding on specific data but attaches the state of the TPM to it. Unsealing (decrypting) the data is only possible if the TPM is in the same state as during the sealing operation.

Today TPM is widely deployed as dedicated chip / module because it does not rely on CPU modifications. Therefore, the security guarantees are weaker compared to SGX. One disadvantage is that the measurement for the remote attestation includes the whole

OS kernel and drivers (which are therefore the Software Trusted Computing Base in the TPC model). With fast changing update cycles it is not possible to keep a list of all possible software configurations. Hence the remote attestation feature of TPM is not widely used.

TPM is used in Microsoft BitLocker drive encryption. The keys are saved in the TPM and only released after the TPM verifies the state of the computer. However, TPM is vulnerable to cold-boot attacks because it releases the keys to the RAM. The encryption and decryption are not executed in the TPM chip itself [19].

#### **Intel Trusted Execution Technology**

The Intel Trusted Execution Technology (TXT) is an hardware-based technology for enhancing server platform security [16]. Especially in highly visualised environments physical isolation of components is not longer possible. Intel TXT is designed to protect against threads by systems that are not in the user's control like the BIOS, hypervisor or firmware.

The Software TCB is smaller compared to the TPM model. It consists of a Virtual Machine (VM) which is hosted using CPU virtualization features. The VM is securely initialized using an authenticated code module and is protected against unauthorized direct memory access (DMA) using a protected range of memory. However TXT does not implement encryption of its DRAM so it is prone to physical attacks on the memory.

Furthermore the software running in System Management Mode (SMM) is not reset during the context switch to the enclave. Multiple times the SMM was compromised which leads to the possibility of accessing the TXT containers memory [13] [62].

#### **ARM TrustZone**

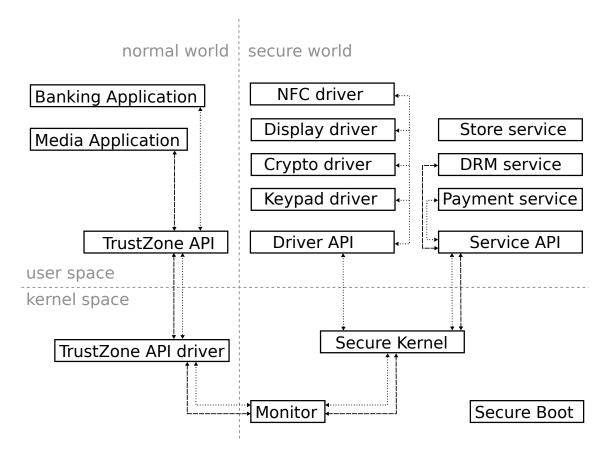

The ARM TrustZone approach to Trusted Computing is based on the concept of a trusted platform which enables infrastructure security by system design [2]. The TrustZone can execute two different systems which are called the non-secure and the secure world. This logical separation is enforced by hardware which is build into system on chip.

When compared to TPM, TrustZone is much more universal usable. By setting the non-secure bit, restrictive policies can be used to manage the access to peripherals. Instead of defining a fixed set of secure functions and protecting a single asset, it is possible to freely implement different security functions in the secure world if needed.

It is possible to implement secure boot sequences in TrustZone. When starting the system, a secure world ROM-based bootloader will initialize a flash device bootloader. The flash-based bootloader will boot the Secure World OS. It is also possible to execute two operating systems beside each other. That is achieved by starting a normal non-secure bootloader after the secure bootloader to boot the normal operating system.

The context switching between non-secure and secure world is managed by a monitor module. The functionality is similar to a traditional OS context switch, but with additional checks and policies when entering from non-secure mode. The monitor is located in the secure world, shielded from possible attacks of the normal world.

**Figure 2.1.:** The software architecture for the proposed DRM and Banking Use-Cases.

ARM proposes Gadget2008 as a possible product design for TrustZone. This design implements secure mechanics for the enforcement of policies for Digital-Rights-Management (DRM) and banking applications. Figure 2.1 shows the applied TrustZone architecture for the Gadget2008.

A DRM service can be placed in the secure world and is therefore secured from manipulation. The media player is placed in the normal world and can be attested by the secure world. Additional DRM data can be also saved in the secure world. When using the media player the DRM service can validate the integrity of the player by attestation. Afterwards the user's licence can be checked at a remote digital content provider service. If the user has the rights to play the media files they can be streamed or decrypted from the local storage.

To secure banking applications a trusted payment service which can access a trusted keypad and display can be implemented in the TrustZone platform. With this technology an application can display transaction details which can be signed by the user via the input of a PIN. Additional security can be achieved by using Near-Field-Communication (NFC) to read data from a physically available bank card. To allow the usage of the NFC or keypad by the normal world low level drivers must be implemented in this unsecured environment. The communication to the secure world can be protected with cryptographic methods when using normal-world device drivers.

#### **Aegis Secure Processor**

Previously described approaches enable authentication of the user and the software. However, they only protect against software based attacks against trusted components and not against physical attacks like tapping or probing chips and busses. The single-chip processor AEGIS by Suh et al. [57] uses additional mechanisms to defend applications against software and hardware based attacks.

The TCB in the AEGIS approach is smaller compared to TXT or TPM. Only the chip itself is trusted, all external modules and peripheries are not assumed to be insecure / malicious. AEGIS implements four different modes which differentiate in the allowed memory access schemes and tamper resistance.

Users can authenticate the CPU via a challenge-response mechanism. The private CPU key is created in-CPU using Physical Random Functions (PRF). Additionally the CPU can sign a hash of trusted operating system components to authenticate them.

Memory protection is enforced by access checks in the MMU and during a secure execution mode using integrity verification and encryption. AEGIS divides the memory into regions with different security guarantees and read / write modes. AEGIS leaves the control of the paging completely to the OS which can exploit the side-channel to learn about access patterns and timing schemes.

#### **Bastion Architecture**

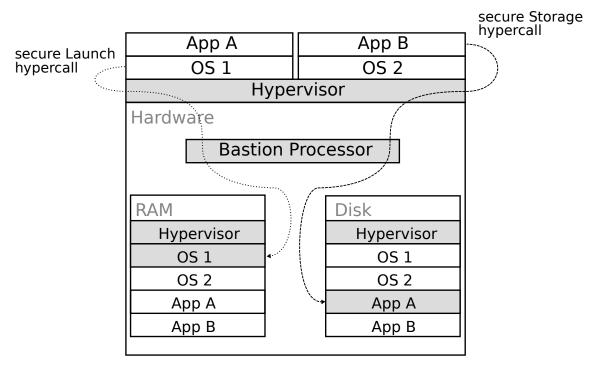

Another approach which defends against physical and software attacks is the Bastion Architecture [8]. Based on a CPU and a hypervisor a secure scalable execution and storage platform is achieved. The Bastion architecture allows the execution of secure trusted containers inside an untrusted operating system and software stack.

First Bastion starts its secure hypervisor by using new functions in the processor. During the so called *Secure Launch* protected memory is allocated for the hypervisor and the integrity of the hypervisor is checked. The hash of the hypervisor is also used for measurement and attestation purposes.

The secure hypervisor can create virtual machines to boot an operating systems. Security-critical operating systems or modules can be started by using the Secure Launch processor feature which requests a protected execution environment from the hypervisor. An overall view on the Bastion Architecture can be seen in Figure 2.2. The integrity of the protected

memory is guaranteed by cryptographic hash trees. Encryption is used to protect the confidentiality of the pages of each launched secured module. The encryption key for the memory protection is generated on each boot cycle. The saved data on the persistent disk is encrypted using symmetric cryptography. The key must be provided by the module that requests the secure storage.

**Figure 2.2.:** The Bastion Architecture with trusted and untrusted components. Trusted components in grey. Secured memory can be requested by special bastion hypercalls.

With Bastion the software TCB only consists of the small hypervisor and not the complete OS (TPM) or the secured OS (TrustZone). Bastion allows the isolation of the secured modules against each other. However, Bastion is also vulnerable against side channel attacks based on memory access schemes.

#### **Compared to Intel SGX**

Different approaches have been developed in the past to achieve the goals of trusted computing which were specified by the Trusted Computing Group.

TPM as standardised and used platform is not able to achieve acceptance because the Trusted Computing Base contains all system software and does not support isolation. The system is either completely trusted or untrusted. In a world of numerous user application, drivers and OS updates that approach is not applicable.

Intel TXT enhances the security of visualisation techniques by using the TPM attestation feature to initialize virtual machines. Like TPM TXT does not protect against physical

attacks on memory or bus.

The Arm TrustZone reduces the hardware TCB to the System-On-Chip. Therefore it is not prone to physical attacks on the peripheries. The main disadvantage of the TrustZone compared to SGX is that TrustZone only differentiates between the secure and non-secure world. The software TCB consists of the complete secure world, including drivers, firmware, secured applications. It is not possible to isolate and defend against threats from components in the secure world. Therefore all secure world components must be trusted.

Aegis is comparable to SGX regarding its independence to trusted system software. Aegis just uses a security kernel module whereas Intel depends on Intel-signed containers( more information about Intel Enclaves in section 2.1.5). Also contains the AEGIS processor a private key which is generated in the CPU. Furthermore, the Intel Skylake CPU includes a private key which is used for attestation and sealing mechanisms.

Bastion and Aegis provide features to allow the attestation of the secure software TCB. Intel SGX is using a hard coded key in the CPU to provide comparable attestation and measurement.

Like Bastion and Aegis, SGX is also encrypting the memory of secured modules. Intel SGX is using the *Memory Encryption Engine (MEE)* described in the paper by [17] and in the ISCA slides [26]. The MEE guarantees the confidentiality, integrity and freshness of the DRAM memory. The MEE is located in the CPU.

Intel SGX also shares the vulnerability to side-channel attacks on memory like Aegis or Bastion [63]. Intel is aware of this and informs<sup>13</sup> the SGX developer about possible side channels. Furthermore, they state that the developer makes sure not to leak any information via side-channels [28].

# 2.1.4. SGX Security Characteristics

As motivation for the following technology section the security properties of SGX will be discussed at first.

Intel also proposed methods to use SGX to deploy trustworthy software solutions [20]. This is achieved by using attestation, provisioning and sealing techniques [1]. With SGX it is possible to create an application which uses an encrypted enclave. This enclave can be measured and its integrity can be attested against a challenging service provider. Via sealing it is possible to encrypt data which can only be accessed by one enclave or all enclaves of the enclave signer.

Intel defines multiple security properties which are achieved by the Software Guard Extensions. [44] [27]

• The enclave memory is secured against observation and modification of any non-enclave party. That excludes virtual machine monitors, ring-0 applications or other

<sup>&</sup>lt;sup>13</sup>https://software.intel.com/en-us/blogs/2015/05/19/look-both-ways-and-watch-out-for-side-channels

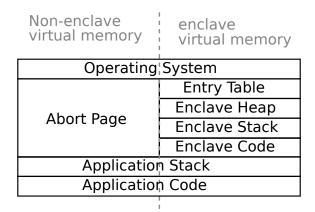

**Figure 2.3.:** The virtual address space layout of the enclave container in the host application.

enclaves. This is achieved by encrypting the memory with a in-CPU *Memory Encryption Engine (MME)* [17]. The encryption key changes every boot cycle.

- Via a hard-coded private key the CPU is able to perform an attestation of itself against a challenger and to sign via public-key cryptography a measurement of an enclave. That can be used to guarantee the integrity of an enclave and for enclave attestation.

- Function calls into the enclave are provided via special instruction which perform checks on the callee and the function arguments. The same applies for function calls from the enclave to the outside. Interrupts and unplanned exits will not reveal secure information because an enclave can only be stopped in a secured area.

- SGX allows the usage of multiple enclave instances which are isolated against each other and from the system software.

- Intel SGX does not protect against reverse engineering and side channel attacks. It is the duty of the enclave developer to withstand these attack vectors.

- The enclave is only debug-able with an special debugger if it is compiled with debugging enabled.

# 2.1.5. Technology

This section gives an overview about the Intel Software Guard Extensions. Most of the theoretical information can be found in the official documentation [27][28][30] and in papers of independent researchers [11].

**Figure 2.4.:** The virtual address space layout of a non-enclave view and as seen from the enclave. Only the enclave can access its protected memory. It is also possible to call untrusted outside libraries from the enclave.

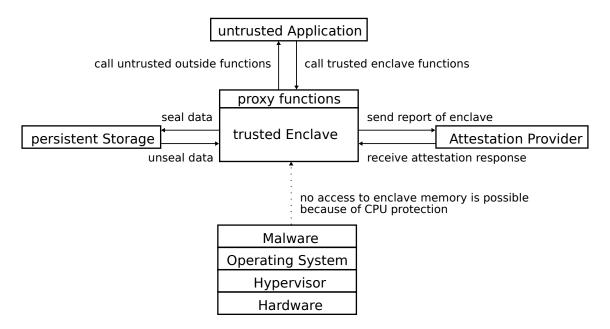

As shown in Figure 2.4 the enclave is seen as a protected container in the address space of the application. SGX guarantees the previously defined security properties to this enclave container.

In the following the architecture of SGX and how the parts interact with each other to achieve the security characteristics will be described. Furthermore, an enclave lifecycle and the building work flow characterised. This section gives an example that helps to understand the measures and actions taken in the SGX implementation of Tresor.

#### **Architecture**

The Intel Software Guard Extensions consist of multiple parts. The basis builds the Intel Skylake CPU with its extended instruction set and memory access mechanisms. These instructions are used to create, launch, enter and exit an enclave, as described in 2.1.5. The protected memory, the *Enclave Page Cache (EPC)*, for the enclave is allocated in the *Processor Reserved Memory (PRM)* and secured with a *Memory Encryption Engine* as described in section 2.1.5.

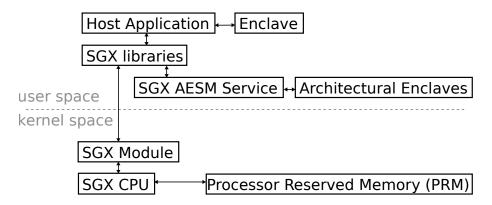

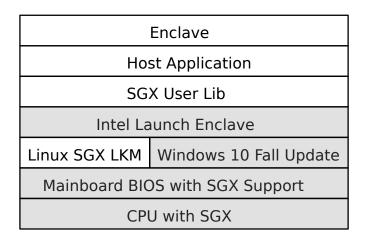

The SGX architecture is shown in Figure 2.5.

The host application is called the untrusted part. The untrusted application can call trusted functions inside the enclave. Neither the input to the enclave, nor the output of the enclave can be fully trusted because a malicious OS can modify these channels. The enclave author has to take this into consideration developing security critical applications.

To initiate the enclave a launch token is needed which can be retrieved with the help of the Intel Launch Enclave. The access to the Launch Enclave and other architectural enclaves (Quoting, Provisioning, etc) is provided by the AESM service in user space. SGX libraries provide the necessary methods to communicate with the AESM Service.

Enclaves can only be entered in user space. However, creating and initiating an enclave

Figure 2.5.: High level hardware and software architecture of SGX.

is only possible in kernel space. Therefore, a privileged SGX module or driver must be installed in kernel space to manage the enclave page cache and calling the specific SGX instructions. The detailed lifecycle of an enclave is described in Section 2.1.5.

The launched enclave can only be entered from an unprivileged user-mode application via special SGX instructions. When the enclave is running, any application which mapped the enclaves page cache into its virtual address space can call enclave functions. When entering the enclave the CPU is switched into *enclave mode* which still runs at user-mode with ring-3 privileges.

# **Memory Usage**

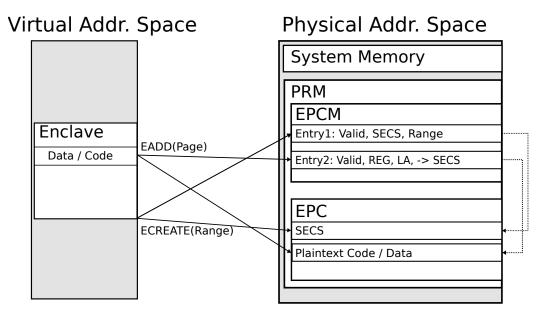

The essential security feature of SGX is that the enclaves data and code is stored, protected and isolated in the *Processor Reserved Memory(PRM)*. The PRM is a range in the DRAM which is protected by the *Memory Encryption Engine (MME)*[17]. This engine rejects *Direct Memory Access (DMA)* on the PRM. The datastructure in the PRM consists of the *Enclave Page Cache Map (EPCM)* and the *Enclave Page Cache (EPC)* itself. The EPC is split into 4 kilo byte pages which are managed in the EPCM and can be assigned to different enclaves. The layout of the physical address space can be seen in Figure 2.6.

The SGX Enclave Control Structure (SECS) is required for each enclave and is saved in the EPC. The SECS represents exactly one enclave and contains enclave information e.g. Enclave ID, Enclave HASH, Enclave Size.

In the EPCM access control and security information for these pages are saved. With these information it is evaluated whether to allow the access to the page or not. The EPCM is managed by the CPU and not accessible by system software. Each EPCM entry contains the following information: the validity of the EPC page, the enclave instance that owns the page (links the the enclave SECS page) and the type of the page (regular Data, Thread Control Structure, Version Array, SECS).

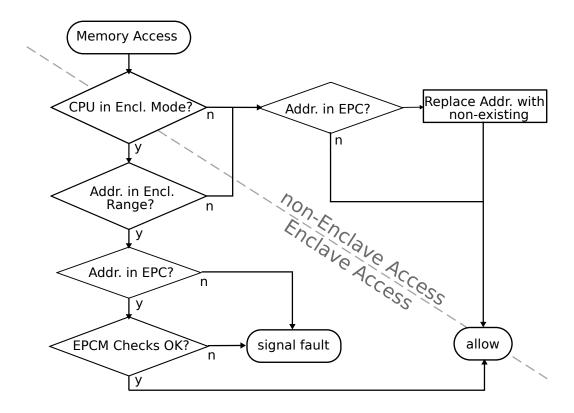

When accessing memory numerous checks are executed. A control flow for in-enclave memory access can be seen in Figure 2.7. External access to PRM is blocked with a

**Figure 2.6.:** Memory mechanisms during ECREATE and EADD.

reference to non existing memory. The following conditions have to be met to allow the memory access. The logical processor must be in *enclave mode*. The page must belong to current executed enclave. Accessed pages need to have a correct virtual address. If the address is not in the enclaves virtual address space and not inside the PRM the access is allowed.

If the CPU is in enclave mode, the address of the page is not in that enclaves memory range but the address is in the EPC, the access is treated like non-enclave to EPC access. In that case nonexisting memory will be referenced. If the CPU is in enclave mode, the address is in the enclave range but the adress is not in the EPC or EPCM checks fail, a page fault will be signaled.

The system software, e.g. the OS or an hypervisor, manages the EPC like normal memory. The os is able to swap out unused pages from the PRM with SGX instructions. The pages on non-PRM DRAM can be swapped with standard mechanisms. Furthermore, the SGX programming model expects the system software to include enclave management functionality which allows the usage of user-mode SGX applications without the need for privileged drivers.

The confidentiality, integrity and freshness of the DRAM data is guaranteed by the *Memory Encryption Engine (MME)*[17]. A normal CPU reads and writes data from its internal cache. If the CPU needs data that is not loaded in the cache, the Memory Controller loads the data from DRAM. The MME extends the Memory Controller and steps in its place when data from a protected region (in SGX the PRM) is accessed. The MME encrypts data before writing, and decrypts data after reading. Additionally, it verifies the data with the help of an integrity tree. The keys used for encryption and authentication are generated at boot time.

**Figure 2.7.:** SGX memory access control scheme.

#### **Enclave Lifecycle**

The new SGX instructions can be separated in supervisor and user mode instructions. A detailed specification of the instructions and the required parameters can be found in the SGX Programming Reference [25]. For further clarification the paper by [11] is recommended.

In the following, an overview of the CPU leaf functions is given. These instructions will be discussed in the next sections. An excerpt of instructions is shown in Table 2.1. To execute the instructions explicit data is needed to perform the security checks and memory allocations.

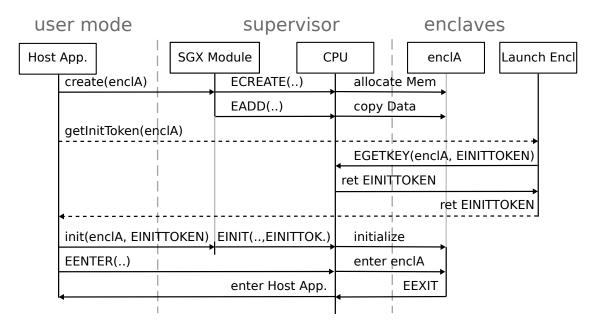

To create and initialize the enclave, the host application hands over the enclave content to a privileged service running in supervisor / ring-0 mode. The Intel SGX SDK provides a SGX kernel module / driver for that purpose. Furthermore, a Launch Enclave is required, because EGETKEY is only callable from an enclave with launch capabilities [25]. In the following a lifecycle of an enclave is described and illustrated in Figure 2.8. The dashed Launch Enclave function calls are simplified for better clarity.

| Mode       | Instruction | Description                 | Explicit Data Structures |

|------------|-------------|-----------------------------|--------------------------|

| Supervisor | ECREATE     | Create an enclave           | PAGEINFO, EPCPAGE        |

| Supervisor | EADD        | Adds a page to the EPC      | PAGEINFO, EPCPAGE        |

| Supervisor | EEXTEND     | EPC page measurement        | EPCPAGE                  |

| Supervisor | EINIT       | Initialize an enclave       | SIGSTRUCT, SECS,         |

|            |             |                             | EINITTOKEN               |

| Supervisor | EREMOVE     | Removes a page from EPC     | EPCPAGE                  |

| User mode  | EENTER      | Enter an enclave            | TCS, SSA                 |

| User mode  | EEXIT       | Exit an enclave             |                          |

| User mode  | ERESUME     | Re-enter an enclave         | TCS, SSA                 |

| User mode  | EGETKEY     | Create cryptographic key    | KEYREQUEST, KEY          |

| User mode  | EREPORT     | Create cryptographic report | TARGETINFO, REPORT-      |

|            |             |                             | DATA                     |

**Table 2.1.:** Subset of SGX Enclave Instructions

**Creating the enclave** An enclave resides in the execution context of a normal host application. These host application must use a privileged party to create the enclave. ECREATE is the first enclave build instruction by that privileged party. It creates a *SGX Enclave Control Structure (SECS)* in the EPC and marks this page it as valid. The SECS>INIT Attribute is set to false because the enclave is not initialised yet. Therefore the enclave can not be executed until the enclave is initialised.

The explicit attribute PAGEINFO of the ECREATE instruction contains information about the enclave (e.g. base address, range). The PAGEINFO will be moved to the page referenced by the SGX Enclave Control Structure (SECS).

**Adding enclave pages** In a second step EADD is used to add more EPC pages to the enclave. EADD can initialize *Thread Control Structure (TCS)* pages or regular code / data pages. The EPCM is updated with the new page entry and a cryptographic log is saved into SECS. Afterwards EEXTEND is executed which measures the added page and adds the result to the cryptographic log in SECS. EEXTEND is also used in software-attestation scenarios.

**Initialising the enclave** The third step is to call EINIT with SIGSTRUCT, SECS and an EINITTOKEN. EINIT finalizes the initialization process and finishes the cryptographic log in SECS. Therefore, no page can be added past EINIT. A hash of the cryptographic log is generated and compared to the hash provided in the SIGSTRUCT. That allows the attestation of the enclave.

The EINITTOKEN is generated by EGETKEY which can only be called from a Launch Enclave. The policy is to allow the execution of the measured enclave (defined via SIGSTRUCT) only on that CPU where the EINITTOKEN was generated. That means

it is not possible to execute an enclave without the prior execution of the Launch Enclave. The Intel Launch Enclave is included in the SGX SDK described in Section 2.1.6.

EINIT is successful if SIGSTRUCT is correctly signed with the public key which is included in SIGSTRUCT, the measurement of the enclave matches the measurement in SIGSTRUCT and the enclaves attributes matches the defined in SIGSTRUCT. Then the sealing identity and enclave identity is saved in the SECS. Finally the SECS->INIT Attribute is set to true and the enclave can be entered.

**Figure 2.8.:** The lifecycle of an enclave. Dashed calls are simplified for better clarity.

**Entering the enclave** The enclave is initialised and can be entered by a user mode application. EENTER uses a pointer from the *Thread Control Structure (TCS)* to an address inside the enclave to transfer control. The CPU switches into enclave mode, saves RSP, RBP for later restore and modifies architectural features registers with enclave values. When entering the enclave the TCS is marked as busy, preventing any other logical CPU to enter the enclave simultaneously.

During the enclave mode an exception, interrupt or VM exit may occur. Instead of transferring the control directly, the enclave state is saved and a synthetic processor state is loaded to prevent data leakage. Then a *Asynchronous Enclave Exit (AEX)* is called, the *Asynchronous Exit Pointer (AEP)* is pushed to IRET and the processor leaves the enclave mode.

When calling ERESUME the AEP will be retrieved from IRET, the enclave registers will be restored and the CPU switches to enclave mode. An exception handler should be implemented in the enclave to prevent ERESUME - AEX loops which are caused by exceptions triggered by the enclave. The host application could call ERESUME with a different AEP to resolve the exception.

Secure data in the CPU registers must be erased during enclave mode because EEXIT does not modify the most of the registers. Furthermore, should the saved RSP and RBP restored to prevent faults.

**Destroying the enclave** An enclave can only be destroyed with the supervisor ER-EMOVE instruction. It deallocates the EPC pages by marking the EPCM entry as invalid if no logical processor is executing the page-owning enclave. After all EPC pages have been set to invalid the SECS page can be removed.

#### **Attestation**

Attestation is a core feature of the trusted computing model. The attestation guarantees the integrity and authenticity of the trusted components by signing an enclave measurement. The measurement of an enclave is the same every time the enclave is initialised. In Intel SGX the EGETKEY and EREPORT instruction are used for attestation [1]. Both instructions can only be executed from inside of an enclave.

To perform an attestation an enclave must be measured and signed. Each enclave contains two signing identities, MRENCLAVE and MRSIGNER.

MRENCLAVE is the identity of the enclave. It is created by using a hash of the internal build log, which was written during ECREATE, EADD, EEXTEND and finalized using EINIT. Therefore MRENCLAVE contains information about the content of the pages, the position of the pages and the security flags. The MRENCLAVE will be the same for every build cycle, if the enclave is not modified.

MRSIGNER is also called the *Sealing Identity*, because it can be used to seal data (see section 2.1.5). The public Key is retrieved of the *Enclave Signature Structure (SIGSTRUCT)*, which consists of information about the Enclave, the value of the expected MRENCLAVE and a public Key of the *Sealing Authority*. Furthermore, is SIGSTRUCT signed with the Sealing Authority's public key, which can be verified. When the value of MRENCLAVE in SIGSTRUCT and the calculated MRENCLAVE are equal the hash of the public Key of the Sealing Authority is saved in MRSIGNER. MRSIGNER is the same for all enclaves, build by the same Sealing Authority. This for example allows updating of the enclave content while using the same encryption key for sealing operations.

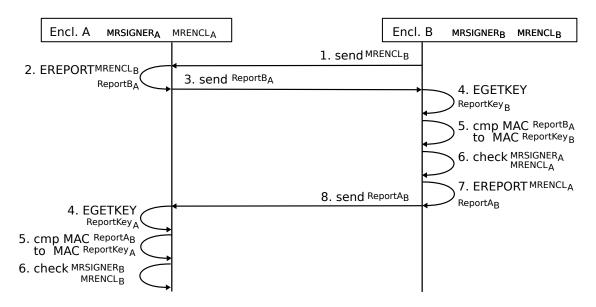

**Intra-Platform Attestation** By using MRENCLAVE and MRSIGNER it is possible to certify the identity of two enclaves against each other to guarantee the integrity and authenticity of the enclaves before negotiating a secret channel.

An Intra-Platform attestation workflow is shown in Figure 2.9. The sequence diagram is minimised to the enclaves only, in reality the communication will be managed by a host application.

Figure 2.9.: Intra Plattform Attestation between two enclaves, communication is simplified.

First the EnclaveB sends its identity (MRENCLAVE<sub>B</sub>) to EnclaveA. EnclaveA calls EGE-TREPORT with MRENCLAVE<sub>B</sub> to generate ReportB<sub>A</sub>, a report of EnclaveB which is signed by EnclaveA. The essence of the ReportB<sub>A</sub> is the signed MAC of the target enclave B, a secret Intel SGX master key and and the SECS attributes of Enclave A. Detailed information about the data flow can be found in [11].

In the third step this is report send to EnclaveB. EnclaveB retrieves its ReportKey to compare its MAC with the MAC in the Report. The MAC guarantees that both Enclaves are running on the same CPU (same secret Intel SGX master key in the CPU) in enclave mode.

In step six the MRENCLAVEA is evaluated with MRSIGNERA. That proofs the authenticity and integrity of EnclaveA. EnclaveB has now successfull been attestated EnclaveA. EnclaveB can now send its ReportAB to EnclaveA. As a result both Enclaves performed the attestation of each other.

**Remote Attestation** Intel proposes a model [1] for remote attestation. Additional Enclaves are required because instead of attesting 2 enclaves at one system via symmetric cryptography, asymmetric cryptography is used for remote attestation. A *Quoting Enclave* is used which verifies an enclaves report. It replaces the MAC of the report with a signature over the report. The signature is generated with a CPU specific private key. The report, also called *Quote*, can send to a remote party for verification.

Intel uses an *Intel Enhanced Privacy ID(EPID)* [7] as anonymous attestation scheme. The EPID bases on a fusekey which is build into the CPU during manufacturing. A database of these fusekeys is maintained by Intel. With the help of a *Provisioning Enclave* an attestation key can be retrieved by Intel's provisioning service [26]. The EPID can be revoked

if the private key of the CPU is considered insecure via the back-end infrastructure.

Costan and Devadas [11] analysed the Remote Attestation feature in great detail. Remote attestation is not in the scope of this thesis and therefore will not be analysed any further.

### Provisioning / Sealing

During enclave execution the data of the enclave is secured with measures described in 2.1.5. When exiting the enclave the pages will be cleared and no enclave state is saved. As described in section 2.1.3 a trusted computing feature is the sealing of data. The integrity and confidentiality of this data must be guaranteed.

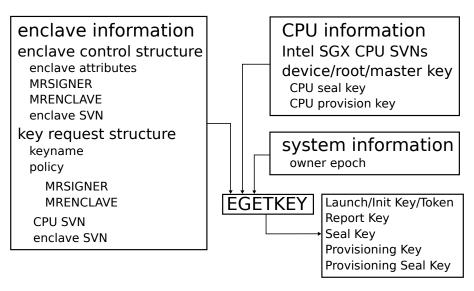

Figure 2.10.: Key hierarchy and generation as described in the Intel SGX manual [25].

Figure 2.10 shows the components which influence the SGX EGETKEY function. It is only possible to generate the same key again if all of the required parameters are the same as in a prior key generation. The key generation process and its consequences for sealed data will be described in the following.

The Intel Skylake Processor contains two different keys for provisioning and sealing. The provisioning key is known to Intel and can be used to encrypt secrets. These secrets which can then be send to the enclave and encrypted during its execution. By using a sealing key, only known to the enclave itself, data can be sealed and unsealed [1]. With EGETKEY the seal and provision key can be retrieved. Intel provides different policies which are bound to the keys usage. These policies are based on MRENCLAVE and MRSIGNER, discussed in 2.1.5.

If EGETKEY is called with the policy MRENCLAVE, it will seal the data specific to the enclave identity. Any change in the enclave will lead to a different seal key. Only this specific enclave instance is able to generate the same seal key again. Therefore, data can be encrypted and decrypted only by this enclave on this single CPU.

MRSIGNER will allow the sealing to the Sealing Identity, the author of the enclave. The generated seal key can be used by multiple enclaves of that enclave signer to access the same data. An applications product ID and a *Security Version Number (SVN)* are included in the sealing identity. The SVN can be used for invalidate old sealed data if a security flaw is patched in a newer enclave version. This sealing model is usefull to allow the usage of data by multiple enclaves.

Personal entropy can be added to the key derivation via the OwnerEpoch value. If the value is changed, the previously generated seal key cannot be generated with the same seal policies again. Therefore, a modification of OwnerEpoch can used to make sealed data on the system inaccessable. OwnerEpoch is loaded into the MSR when SGX is booted [25].

The official documentation of SGX [25] describes the key hierarchy briefly. A in-CPU key is used as unique root key of the key hierarchy. The keys which are returned by the EGETKEY instructions derive from that key. Costan and Devadas [11] describe the root key as SGX Master Derivation Key, which is used in all key derivation processes. That leads to the assumption that a sealed secret can not be encrypted by the same enclave on another CPU because the root key differs.

### 2.1.6. SGX SDK

The Intel SGX SDK provides tools to build and execute enclaves. As described in 2.1.5 an Intel Launch Enclave is needed to generate the launch key for a custom enclave. The Launch Enclave is an Intel Architectural Enclave. The following enclaves are included in the SDK.

- Launch Enclave measures custom enclave and provides launch key / EINIT token for it. Used for licensing purposes in the future.

- Quoting Enclave signs a report of an enclave with the platform specific Intel EPID key which can only be accessed by the quoting enclave. Used during remote attestation.

- Provisioning Enclave Proofs its identity to the Intel Provisioning Service to receive attestation key. That key is send to the Quoting Enclave for remote attestation.

- Platform Service Enclaves are used for pairing and protected session management. Also used for remote attestation, only briefly described in [27]

The architectural enclaves can only be entered from the user mode. Therefore, the SDK includes the AESM service / daemon which manages the enclaves. In addition, the AESM service includes a database for the Platform Service Enclave. This database contains tables with information about nodes, MRSIGNER and other data. This includes the service a public key for provisioning and an white list certificate. No further explanations regarding these files could be found.

The communication between the custom host application, which enters the enclave and the AESM service is established by the SGX libraries. A subset of the libraries that are included in the SDK.

- sgx\_trts SGX internals

- sgx\_tstdc standard C library

- sgx\_tservice sealing, architectural enclave support

- sgx\_tcrypto cryptographic library

- sgx\_urts enclave management library, creation and entering from host application

To provide SGX functionality in the kernel space the SDK also contains a kernel module / driver. That module manages the enclave page cache (EPC) management.

### **Enclave Building**

Intel published the Intel SGX Evaluation SDK tools to build the encrypted enclave containers and the matching application. The SDK consists of multiple tools which allows the building, measuring, debugging and configuration of enclaves.

- Edger8r Tool analyses the enclave's EDL file and generates interfaces and proxies between the trusted enclave and untrusted application

- Enclave Signing Tool generates metadata such as the enclaves signature and adds the metadata to the enclave

- Debugger supports the analysis of enclaves with active debug flag

- Memory Measurement Tool analyses the memory usage of the enclave

- CPUSVN Configuration Tool used to configure the security version of the CPU which affects its key derivation process

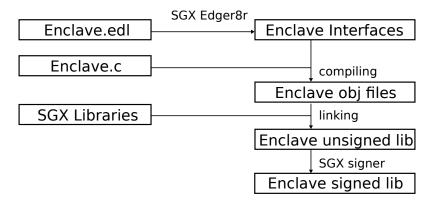

**Building Workflow** Enclave Generation is the building of the enclave container and the application with the SGX SDK. The application is the untrusted non-encrypted part which starts the enclave. Enclave creation is the process in the application itself which launches the enclave.

To generate a running enclave with the Intel SGX SDK following files are required.

- Intel SGX SDK include files especially the sgx\_urts which is used by the application to create and launch the enclave

- Intel SGX SDK library files especially the sgx\_edger8r and sgx\_sign

- Intel isgx Kernel Module for executing the new SGX instructions and management of the EPC

- Application source file

- Enclave source and EDL file

In Figure 2.11 the building workflow is visualised. The enclave EDL file is parsed by the Edger8r which generates the Enclave Interface files. The generated interface definitions and implementations are used by the enclave and the host application for communication. The SGX Libraries are required during the linking. The generated library is called an unsigned library. By using the SGX signer a certificate of the enclave and its configuration is created. The generated enclave library is signed and can be used in an host application.

Figure 2.11.: The building workflow with the Intel SGX SDK.

In the following, an example demonstrate the building of an Enclave and its application. The enclave offers a trusted function which changes a *char array*.

**EDL file** describes the interfaces between the enclave and the untrusted application. It is read by the edger8r tool which generates the edge routines for the interfaces.

The EDL file is divided in an trusted (enclave) and untrusted (application) part. The return value, function name and parameters are user defined. If another return value than void is defined, the value can be retrieved in the function call as 2nd parameter. An example EDL file is shown in Listing 2.12.

The following parameter definitions are available:

Figure 2.12.: Enclave.edl interface definitions

- user\_check the pointer wont be verified by SGX. Neither is the content of the buffer copied into the enclave. The user is in charge of the check and memory operations.

- in During ECALL, the buffer and content will be located inside the enclave. During OCALL, the buffer will be copied from the enclave to the application.

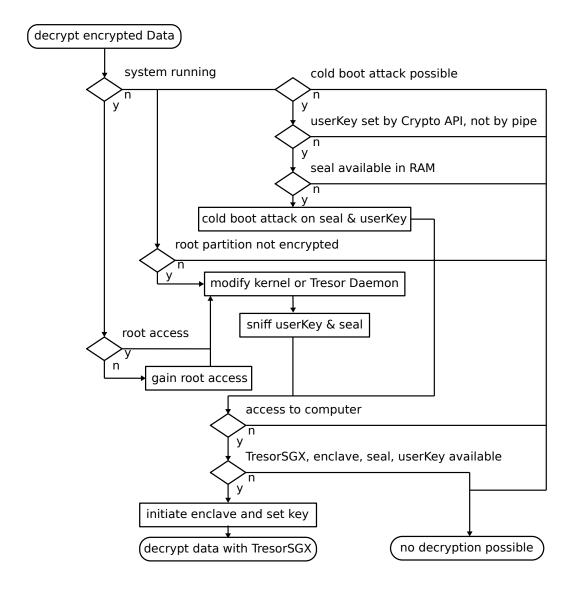

- out During ECALL, buffer will be allocated and can be used by enclave. On the function return the buffer will be copied to the outside application. During OCALL, the untrusted buffer from the application will be checked and copied into the enclave.